Along with the progress of our

chipset partner vendor, H3 is entering the development phase of the CXL 2.0

Memory Pooling solution on Apollo B0 features. H3 is also collaborating with a

globally recognized hyper-scaler enterprise to test the cutting-edge solution

aimed at optimizing internal IT infrastructure and enhancing utilization

efficiency to improve its global competitiveness.

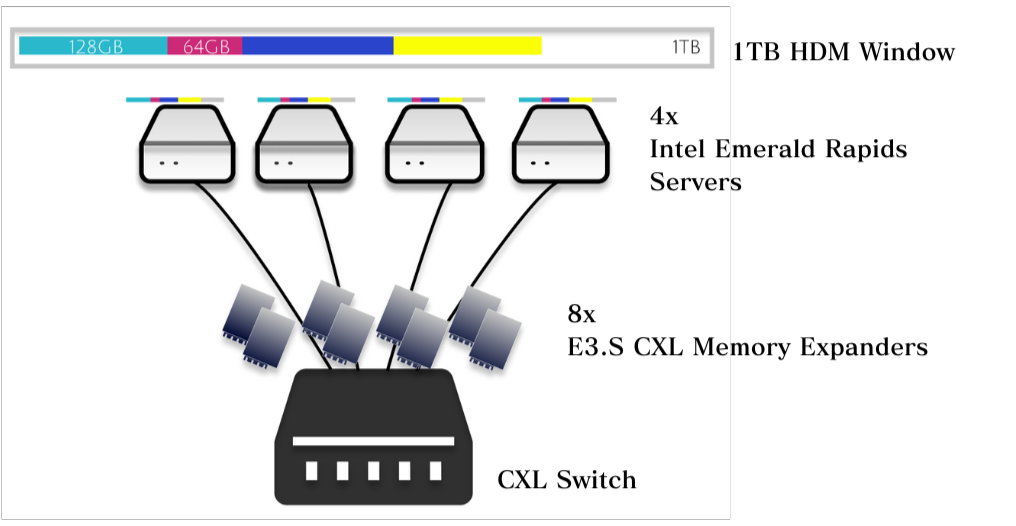

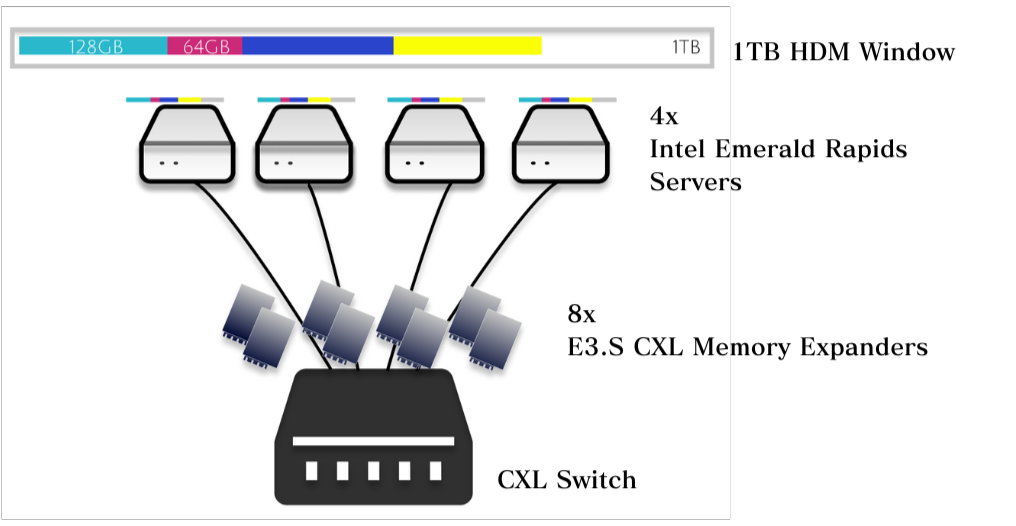

At present, H3 has enabled memory

pooling and sharing with 1TB of memory. By using Intel Emerald Rapids CPUs in

four host servers connected to eight E3.S memory cards through the CXL switch,

users can monitor memory usage through the 1TB HDM window.

Users can dynamically allocate memory in 64GB-based units within the HDM window for their applications. Once application tasks are completed, the management center can reclaim the memory resources and reassign memory to the next waiting application. All these processes applied to downstream devices can be observed through the window in each host, with a CXL switch intermediating the high-speed communication in a minimized latency. This represents a significant leap compared to traditional Ethernet-based data transmission.

With these features, resource

managers can obtain a comprehensive overview of how all memory resources are

used, enabling administrators to make more informed decisions regarding

resource allocation. Even a minor change can have a significant impact.

Both internally and externally shared cloud resources can reap the benefits of

memory pooling for improved overall infrastructure utilization efficiency. A

reduction in the Total Cost of Ownership (TCO) is on the horizon. We

anticipate the release of additional testing benchmarks shortly to showcase its powerful performances and expect a

more agile allocation with a smaller memory unit on the B0 chip!